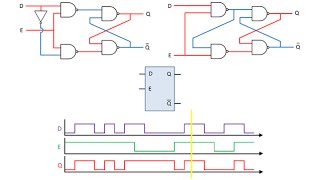

This is the third in a series of videos about latches and flip-flops. These bi-stable combinations of logic gates form the basis of computer memory, counters, shift registers, and more. In particular, this video covers the gated D latch, otherwise known as the data latch or simply the D latch. It begins by reviewing the gated SR latch, including the risk of making both inputs high at the same time which results in a race condition and therefore an unpredictable state. It then shows how this problem can be overcome by a gated D latch. Two ways of building a gated D latch are covered and its behaviour is illustrated with a timing diagram. The videos that follow this one build upon the principles covered here and include the clocked D latch, edge triggered pulse latches and the master slave D type flip flop.

![অধ্যায় ০১ - রসায়নের ধারণা - রসায়ন পরিচিতি - ২ [SSC]](https://i.ytimg.com/vi/8QjH_EFBb5I/mqdefault.jpg)

![অধ্যায় ০১ - রসায়নে অনুসন্ধান বা গবেষণা প্রক্রিয়া, রসায়নে পরীক্ষাগার ব্যবহার [SSC]](https://i.ytimg.com/vi/PAqrSt9pD2Y/mqdefault.jpg)